【48812】VGA的驱动显现以及逻辑分析仪的运用

来源:米乐官方入口

发布时间:2024-08-02 14:56:35 1

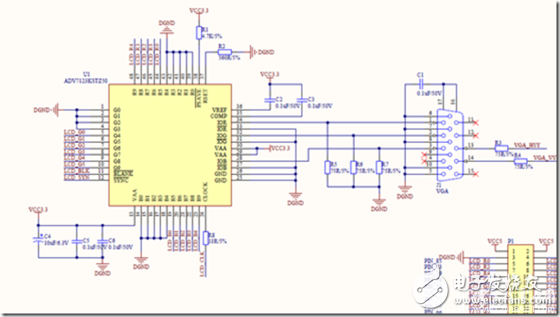

的进程,开发环境为Vivado 2016.2。Zedboard是经过权电阻网络来建立的DAC电路,

程序中是经过计数器来模仿发生行、场同步信号。这儿首要介绍下Vivado的开发流程。Vivado下新建工程,挑选开发板Zedboard,如图:

将修改好的工程代码都加进来,这儿经过clock Wizard从头生成所需求的时钟,办法和quartus迥然不同,移植好的工程如图:

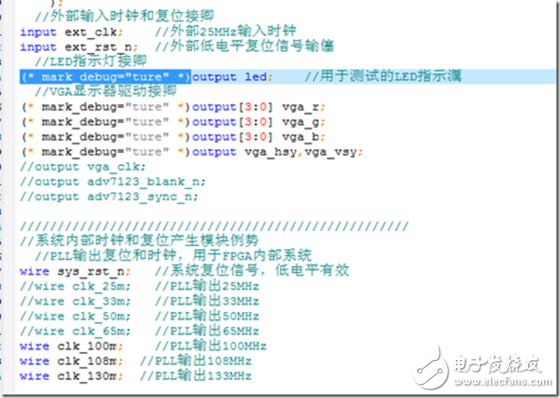

然后履行Run Synthesis、Run ImplementaTIon和Generate Bitstream就可以生成.Bit文件下载到FPGA里了。这儿我又想用下在线逻辑分析仪的功用,那么第一步是要在代码里对需求检查波形的信号前加(* mark_debug=ture *),就算该信号在工程中没有衔接,也不会别编译器优化掉。如图:

咱们将要在逻辑分析仪中调查VGA的红、绿、蓝信号。挑选Set Up Debug,将感兴趣的信号加进来。